三星4纳米和台积电4纳米差距?

三星4纳米和台积电4纳米差距?

三星4纳米和台积电4纳米有差距。

首先要说台积电的4纳米还未量产,目前没法比较,但可以从过往芯片性能推算。第一是技术差距,虽然三星和台积电最新工艺都是5nm,但在业内人士眼中,三星5nm工艺与台积电6nm工艺是同一水准。第二点原因是台积电技术升级换代快,能生产先进芯片的产线数量更多,能为公司创造更高的利润,台积电有成本优势。第三点原因是台积电拥有质量更高的客户,并且客户能够给予台积电稳定的订单。所以台积电研发比较稳定。

三星4nm LPE工艺其实是基于5nm的第三代5nm方案改名版。相比5nm第三代技术,4nm LPE在性能并没有很明显的提升,之所以改名,主要是为了容易做营销。

台积电在2021年技术论坛上公开宣布,4nm工艺预计2021年第三季度进入试产阶段,相比此前的计划提前了一个季度的时间。

台积电的进度加快的同时,一直在追赶台积电的三星,也被曝出了有关4nm技术的消息。

台积电的4纳米领先三星4纳米。

在光刻机数量、使用熟练度都落后的情况下,照此发展,三星4纳米与台积电4纳米的差距将会越来越大。台积电提前试产4纳米在笔者看来,台积电之所以每次都能在先进制程芯片的量产上,快三星一步,或许也有EUV光刻机方面的原因

4nm芯片是什么水平?

4nm芯片属于目前最顶尖的技术水平!

芯片最高端的要数手机芯片,目前可以量产的手机芯片4nm是骁龙8gen1和联发科9000,目前两款手机芯片是目前最顶级的手机处理器,安兔兔跑分可以超过一百万,和苹果A15的处理器差不多!

所以,4nm芯片是顶尖水平!

台积电 4nm 制程工艺,本质上属于 5nm 加强版,它的全名也叫 5nm N4 工艺,实际性能与苹果采用的 5nm+ 工艺。因此,联发科 4nm 工艺新芯片理论上没有机会赶超苹果,它真正的对手,应该是高通骁龙 888。等到联发科新芯片问世,很可能将超越骁龙888,成为安卓手机中最好的芯片!

摩尔定律说硅基芯片的物理极限是7nm,为什么台积电还能做出5nm的芯片?

感谢您的阅读!

【别把摩尔定律神化,未来的台积电还能有0.1nm的工艺制程】

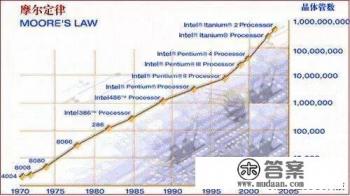

摩尔定律是什么?当价格不变时,集成电路上可容纳的元器件的数目,约每隔18-24个月便会增加一倍,性能也将提升一倍。它只是一种商业观测或推测,并非是物理定律!它只是一种预测数据,这种数据的准确性随时在接受打破!

那么,台积电5nm工艺是什么?实际上,台积电5nm技术是在7nm基础上微缩的全节点工艺,因为使用了极紫外(EUV)光刻技术,并且在总掩模数量上,进行缩量,这就让5nm比以前的7nm节点少几个掩模。

并且,根据推测,5nm一方面功耗更低,比如相同速度下的功耗降低了30%。

其实,不仅仅是5nm,台积电还在不断的加大对于3nm的研究,它将用150亿美元用于投资3nm工艺制程。

据说,3nm工艺(N3)的晶体管密度将提升约70%,速度提升10%到15%,芯片的性能提升25%到30%,3nm工艺可能让台积电的技术更上一层楼。

而且,有消息称,台积电在2050年能够实现0.1nm的氢原子尺度。

当然,所谓的摩尔定律实际上就是一种预测,你现在来看也能知道它的定律一直在被打破,因此更加证明它只是一种一定时间内的猜测而已。代工企业为了能够提升性能,只会打破这种所谓的束缚,台积电如是!国内的代工企业也应该有这份努力,打破束缚。

摩尔定律指的是在价格不变的情况下,芯片上可容纳晶体管数目,约每隔18-24个月便会增加一倍,性能也将提升一倍。

从当前芯片制造来看,要实现摩尔定律,芯片制造工艺必须不断提升。工艺节点从90nm、65nm、40nm、28nm、16nm到现在的7nm,芯片厂家不遗余力地减小晶体管栅极宽度来达到工艺的升级,但到了7nm之后,晶体管的漏电问题越来越严重,单纯靠减少晶体管栅极宽度的方法已经无法提升芯片制造工艺。

这个时候各厂家各显神通,采用不同的方法解决漏电问题。intel的高介电薄膜、SOI、鳍式场效电晶体技术等等技术应运而生。不过难度越来越大,各大厂家受阻严重,GlobalFoundaries放弃7nn研发,intel的10nm一推再推,目前7nm量产顺利的主要就是台积电和三星了。

台积电的5nm预计明年Q1量产,华为的最新麒麟990预计将采用5nm工艺。而最新的新闻,台积电的3台积电的5nm预计明年Q1量产,华为的最新麒麟990预计将采用5nm工艺。而最新的新闻,台积电的3nm工艺已经启动,预计2022年量产,后面的工艺进步越来越难,需要新的技术上的突破。

在集成电路工业领域,有一个神奇的定律归纳了其发展规律,即集成电路上可容纳的晶体管数目,每隔 18-24 个月便会增加一倍,性能也将提升一倍,这就是广为熟知的“摩尔定律”。

摩尔定律是什么

摩尔定律是由英特尔(Intel)创始人之一戈登·摩尔(Gordon Moore)提出来的。其内容为:当价格不变时,集成电路上可容纳的晶体管数目,约每隔18个月便会增加一倍,性能也将提升一倍。换言之,每一美元所能买到的电脑性能,将每隔18个月翻两倍以上。这一定律揭示了信息技术进步的速度。

众所周知,目前通信行业使用的的半导体大部分都是硅基电路,并验证了摩尔定律2年一次的微缩规律。从当前芯片制造来看,要实现摩尔定律,芯片制造工艺必须不断提升。工艺节点从90nm、65nm、40nm、28nm、16nm到现在的7nm,芯片厂家不遗余力地减小晶体管栅极宽度来达到工艺的升级。

摩尔定律过去是每 5 年增长 10 倍,每 10 年增长 100 倍。而如今,摩尔定律每年只能增长几个百分点,每 10 年可能只有 2 倍。

台积电董事长张忠谋应交大EMBA之邀,发布演说的时候表示:2017年,台积电制程已演进至10nm,2018年要量产7nm,5nm则将依序接后。3nm的发展时间基本上已经有一定的计划了;按照台积电的内部规划,今年将会正式量产5nm工艺、明年则是3nm工艺,而2nm工艺已处在研发阶段,目前计划在2024年公布面世。

人工智能时代下的摩尔定律随着工程技术的改进,我们终将碰上物理学上的瓶颈。人工智能时代的到来极大地促进了集成电路产业的发展,S场不断扩大,技术不断创新,所有的一切让摩尔定律足足持续了 50 多年。摩尔定律还会走多远,是否会有新定律诞生呢?

摩尔定律是由英特尔(Intel)创始人之一戈登·摩尔(Gordon Moore)提出来的。其内容为:当价格不变时,集成电路上可容纳的元器件的数目,约每隔18-24个月便会增加一倍,性能也将提升一倍。

从以上可以看出,“”摩尔定律“”并非一个科学理论,而是个人主观臆断。在近半个世纪几乎符合这个判断,但进入21世纪以来,芯片的制造的速度放缓,性能提升更是缓慢,是这个推断已经破产。

从理论上,这种推断也是站不住脚的,凡事都有个极限,当越接近极限更进一步就要比前面困难得多,所需的时间也更长。

芯片的制程,如提问中的硅5纳米,和摩尔定律没有任何关系,尽管摩尔定律是一个错误的个人臆断。

芯片上集成了太多太多的晶体管,晶体管的栅极控制着电流能不能从源极流向漏极,晶体管的源极和漏极之间基于硅元素连接。随着晶体管的尺寸逐步缩小,源极和漏极之间的沟道也会随之缩短,当沟道缩短到一定程度时,量子隧穿效应就会变得更加容易。晶体管便失去了开关的作用,逻辑电路也就不复存在了。

据业内人士分析,“台积电的3nm制程,很可能才是在摩尔定律下最后的工艺节点,并且台积电的3nm工艺会是关键的转折点,以衔接1nm工艺及1nm之下的次纳米新材料工艺”。

台积电的创始人兼董事长张忠谋也表示,摩尔定律在半导体行业中起码还可存续10年,这其中就包括5nm工艺、3nm工艺,而台积电会不会研发,以及能否研发出2nm工艺,则需要再等几年才能确定。

最后要说的是,即便硅基芯片终有一天非常非常地接近物理极限,人们还可以寻找到其他如采用新材料等技术路径来驱动计算性能持续提升。

在半导体行业,所谓工艺极限是特定而相对的,特定指的是7nm极限是在半导体FinFET工艺下的物理极限;而相对的意思是每次遇到瓶颈的时候,工业界都会引入新的材料或结构来克服传统工艺的局限性。

10年前我们遇到了65nm的工艺极限,工业界引入了HKMG,用High-K介质取代了二氧化硅。

5年前我们遇到了22nm的工艺极限,工业界发明了FinFET和FD-SOI,前者用立体结构取代平面器件来加强栅极的控制能力,后者用氧化埋层来减小漏电。

现在7nm是新的工艺极限,工业界使用了砷化铟镓取代了单晶硅沟道来提高器件性能。

当然这里面的代价也是惊人的,每一代工艺的复杂性和成本都在上升,现在还能够支持最先进工艺制造的厂商已经只剩下Intel、台积电、三星和GlobalFoundries了。

至于7nm以下,就要依赖极紫外(EUV)光刻机了。

台积电投资28纳米芯片生产线是不是要禁止?

必须禁止🚫!台积电南京28.87亿美元上台湾淘汰下来的28纳米,美国120亿美元上先进的5纳米,目的一目了然!目前国内芯片产能集中在28附近,台积电这样摆明了就是利用台北淘汰的旧设备和国内外资的优惠条件低价打击国内公司,变相配合美国!国内挣钱去补贴投资美国的5纳米线!国内公司没有足够的S场和利润怎么去发展更好的技术?如果南京批了就是助纣为虐!资本本质上说台积电是美国企业永远不会成为自己人!美国人的资本加上中国人的智慧,这种往往是更很更致命的,万万不能被它迷惑了眼睛!

芯片5nm和7nm有什么差别?CPU已经很小了,可以做大点吗?

你的问题很好,问到关键点了。

已经足够用。无论5G手机,还是其它用途,完全可以满足需要。最为典型的就是北斗卫星芯片24纳米都没有问题。金融系统,工业系统亦如此。所以,美国的制裁,对军工,工业,金融网络教学等等没有任何影响。

轻薄化手机。主要是手机需要最轻最薄而且功能强大,用途广泛。所以,特朗普扼杀的是华为高端芯片,其实对华为的5G基站都没有任何影响。

中科院开始发力。中科院院长召开新闻发布会,表示着力研发光刻机,高端芯片等等掐脖子项目。举国体制➕企业积极参与的新一轮科研浪潮已经扬帆起航,我们拭目以待吧!

当前Intel I9处理器仍然在使用14nm工艺制作,而手机芯片却已经做到了7nm,难道手机芯片比Intel芯片技术先进吗?

nm是长度单位,1纳米=0.0000001厘米,在芯片制造领域,纳米代表了一个工艺节点的物理长度。在同样大小的一颗CPU上,5nm制程工艺将可以容纳更多的工艺节点。

2018年,华为在德国柏林正式发布了麒麟980处理器,这是全球首款使用7nm制程工艺的处理器,凭借着这颗处理器的出色表现,缩小了与世界顶级手机CPU制造商的差距,甚至在单核处理能力方面一度超越。这也开启了华为在手机S场的新时代,让某些国家感受到了极大的危机。

手机制程芯片越小越好吗?当前来看,确实如此!

因为在过去的一年里,后置四摄、5G芯片、双扬声器、升降摄像头等功能,被添加进这小小的手机中。而从人体工程学的角度来看,手机的体积不可能再增加。要让手机实现更多的功能,只有减少硬件体积,这是摆在手机设计师面前的一大难题。

与手机CPU设计面临的局面不同,桌面电脑的功能设计已经相对稳定,在CPU设计方面不需要为捉襟见肘的硬件空间发愁,所以Intel没有必要把精力放在制程工艺的提升上。

今天非常巧合,看似不相关的两则新闻值得关注:

一是:高通骁龙5nm处理器骁龙875被曝光;

二是:华为宣布“愿意使用高通芯片!!”;

在当前焦灼的世界环境下,您有看出什么端倪吗?

文/小伊评科技

在解答这个问题之前我们首先要知道芯片工艺的提升代表的是什么。

如果我们用显微镜来观察一枚芯片的话,芯片内部其实是由数十个甚至数百亿个晶体管所构成,而一款CPU之所以能够拥有运算能力和这些晶体管是息息相关的。

所以大家可以看到,每一代处理器的升级,芯片厂商都会着重的提到晶体管的数量,比如苹果最新发布的A14处理器的晶体管数量就从A13的85亿提升到了118亿,这就是工艺提升所带来的直接结果——晶体管数量的提升,而晶体管就是决定处理器综合算力的决定性因素之一。

每一个晶体管最重要的结构就是门电路,这些门电路说白了就是一个又一个的电路开关,而通过开关的闭合和放开(对应编程语言的0和1),从而实现各种门电路逻辑以处理不同的事件,常见的有与门、或门、非门、与非门、或非门、与或非门。

而目前我们常见到的所谓5nm,7nm等工艺说白了其实就是指每一个晶体管上门电路的宽度,门电路体积越小,晶体管的体积也就越小,单位体积内所能放下的晶体管数量也就越多,而工艺提升的本质就是降低门电路的宽度 。

这么说可能有些枯燥,为了方便大家理解,我们把CPU的性能表现比作是一家工厂的产能,把晶体管比作是一条完整的产线,每一条产线都拥有一模一样的产能,把芯片的面积比作是工厂的占地面积。

那么在其他因素排除的情况下,这家公司所拥有的产线越多其产能肯定也就越高,但是这家工厂的面积是无法提升的,那么如何在相同的厂房面积下放下更多的产线呢?答案就是降低产线的体积,而工艺提升的本质为了降低这些产线的体积而来。

而且工艺的提升所带来的好处还远不止如此。

当晶体管缩小之后,晶体管之间的电容也会降低,晶体管的开关频率也得以提升,从而使整个芯片的工作频率就上去了,所以每一次工艺升级都伴随着处理器频率的提升,如下图所示,麒麟系列处理器的大核主频一代比一代高。

除此之外,晶体管体积降低之后还能有效地降低电流再通过他们时的内阻,提升了核心的能效比从而降低了整体的功耗,反应到我们消费者实际体验这方面就是芯片更S电而且发热更低了。

所以芯片工艺的提升对于芯片总体实力的提升是非常巨大的,这一点也是毋庸置疑的。根据台积电的数据来看,5nm工艺相比于7nm可以将晶体管密度增加20%,而在同样密度和频率下功耗可降低10%,提升也是比较明显的。

芯片为什么不能做大?

那么有人会问了,既然芯片的性能和晶体管的数量息息相关,那么为什么我们不能把芯片的面积做大呢?首先芯片做大确实有利于性能的提升,这是毫无疑问的,下图最左侧的就是当年民用领域面积最大的芯片——AMDThreadRipper 1950X,相比于其他芯片整整大了一大圈,性能当然也非常恐怖,但是价格也相当昂贵,当年的S售价格高达999美元(约合6750美元),性能强么?确实强,但是并不实用。

你能想到的芯片厂商都能想到,芯片不能做大是有很多原因的。

首先是外部设备体积限制,就拿大家最常见的手机来说,其体积最大也就只有7英寸左右,再大就不方便携带了,那么在这种情况下芯片体积如果做得过大的势必会影响手机的体积和厚度,其结果往往是得不偿失的,大家思考一下,如果一款手机的尺寸和iPad差不多大你能接受么?估计绝大多数人都无法接受。

其次还有成本的问题,CPU的体积越大,消耗的硅晶圆,每一片晶圆所能产出的成品芯片的数量就越小,浪费也就越大。而且CPU的面积越大,其出现问题的概率也就越多(和公司越大问题越多是一个道理)良品率就越低,那么在这两个因素的共同影响下,芯片的体积做的越大成本会指数级的增长,这些成本的提升最终都会转嫁到消费者头上,那么你能接受么?

最后还有就是延迟的问题,芯片的体积越大,电信号传递的距离也就越远,那么在这种情况下一条指令从下达到处理器处理完成返回的事件就会非常长,这是物理性质所决定的,而且想要提高频率必须要加大电压,那么芯片的功耗就会上升,最后的结果就是性能没提升多少,功耗提了不少,得不偿失。

end 希望可以帮到你

版权声明

本文仅代表作者观点,不代表木答案立场。